For example: for vital signs monitoring and gesture recognition, IMEC has developed a 140GHz FMCW radar transceiver with an on-chip antenna. The radar has a working range of 0.15m to 10m, a resolution of 11mm, a radio frequency bandwidth of 13GHz, and a center frequency of 145GHz. The transceiver IC is manufactured using 28nm module CMOS technology, which can realize a low-cost solution.

Introduction

The millimeter wave semiconductor is the basic device of the fifth generation mobile communication technology (5G), and the technology of using millimeter wave frequency for directional communication is one of the key technologies of the expected 5G configuration. The frequency range of millimeter waves is 30 to 300 GHz. The bands currently studied include 28 GHz band, 38 GHz band, 60 GHz band and E band (71-76 GHz, 81-86 GHz). 5G technology shifts the communication frequency band to millimeter wave frequencies much higher than the fourth-generation mobile communication technology (4G). Compared with 4G, the spectrum bandwidth of 5G will be increased by 10 to 20 times, the maximum data transmission rate can be increased by 20 times, and the size of antenna array and base station equipment is smaller and the cost is lower. Among the millimeter wave frequency bands, the 28 GHz frequency band and the 60 GHz frequency band are the two most promising frequency bands for 5G applications.

As a passive component for sending and receiving RF signals, the antenna determines communication indicators such as communication quality, signal power, signal bandwidth, and connection speed, and is the core of the communication system. How to increase spectrum data throughput is a major challenge from 4G to 5G. The key technology of 5G is the massive multi-input, multi-output (MIMO) integrated millimeter wave antenna technology. Each MIMO channel has its own signal path from the receiving antenna, the transmitting antenna to the microprocessor. The function of the receiving channel is to realize the down-conversion from the RF signal received by the antenna to the input sampling baseband frequency, and functions such as analog-to-digital signal conversion. The function of the transmit channel is to convert the up-converted digital signal into an analog RF signal. Downsizing is an important challenge for 5G antennas. The smallest base station antenna size will shrink to the size of a credit card, which will increase the integration, low power consumption and connectivity requirements of millimeter wave antennas and circuits. Improving power density is another important challenge for 5G antennas.

Multi-antenna system integration is one of the key technologies to deal with the challenges of 5G system MIMO, downsizing, and increasing power density. Since SiGe and CMOS RF integrated circuits have reached high fT, fmax and high integration density, CMOS, SOI and SiGe processes can be used to design large-scale fully integrated silicon millimeter wave phased array circuits. Based on the full RF structure, 8-32 yuan transmit (Tx), receive (Rx) or receive/transmit (T/R) modes have been successfully used in the 45-110 GHz frequency band. The silicon integration solution can integrate multiple components on the same chip. Compared with Group III-V semiconductor technologies such as GaAs and InP, silicon-based technologies have higher integration and lower costs. Silicon phased array chips are widely used in the millimeter wave field. The challenge faced by this technology is that the RF power amplifier, low-noise receiver amplifier, A/D converter or D/A converter on the signal chain unit all require great efficiency improvements.

Both wireless communication and sensor systems can improve performance through the use of RF systems to improve integration and the use of new packaging technologies. There are currently three schemes for realizing front-end circuits and integrated antennas. The first is the antenna packaging (AIP) technology, where the antenna is manufactured using IC packaging technology. The second is the antenna on chip (AoC) technology, where the antenna is directly fabricated on a silicon substrate. The third is a hybrid technology of AiP and AoC. The antenna feed point is made on the chip and the radiating element is realized off-chip. In AiP technology, the interconnection of the chip and the antenna should achieve effective signal transmission efficiency within a certain frequency range. The main packaging processes include wire bonding and flip chip technology. However, the loss of the device at high frequency is large, and the cost will increase.

1 Structure of phased array receiver

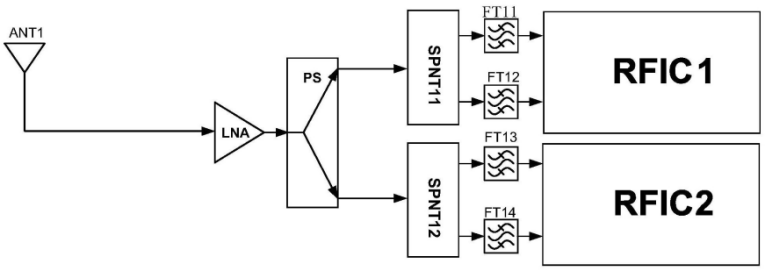

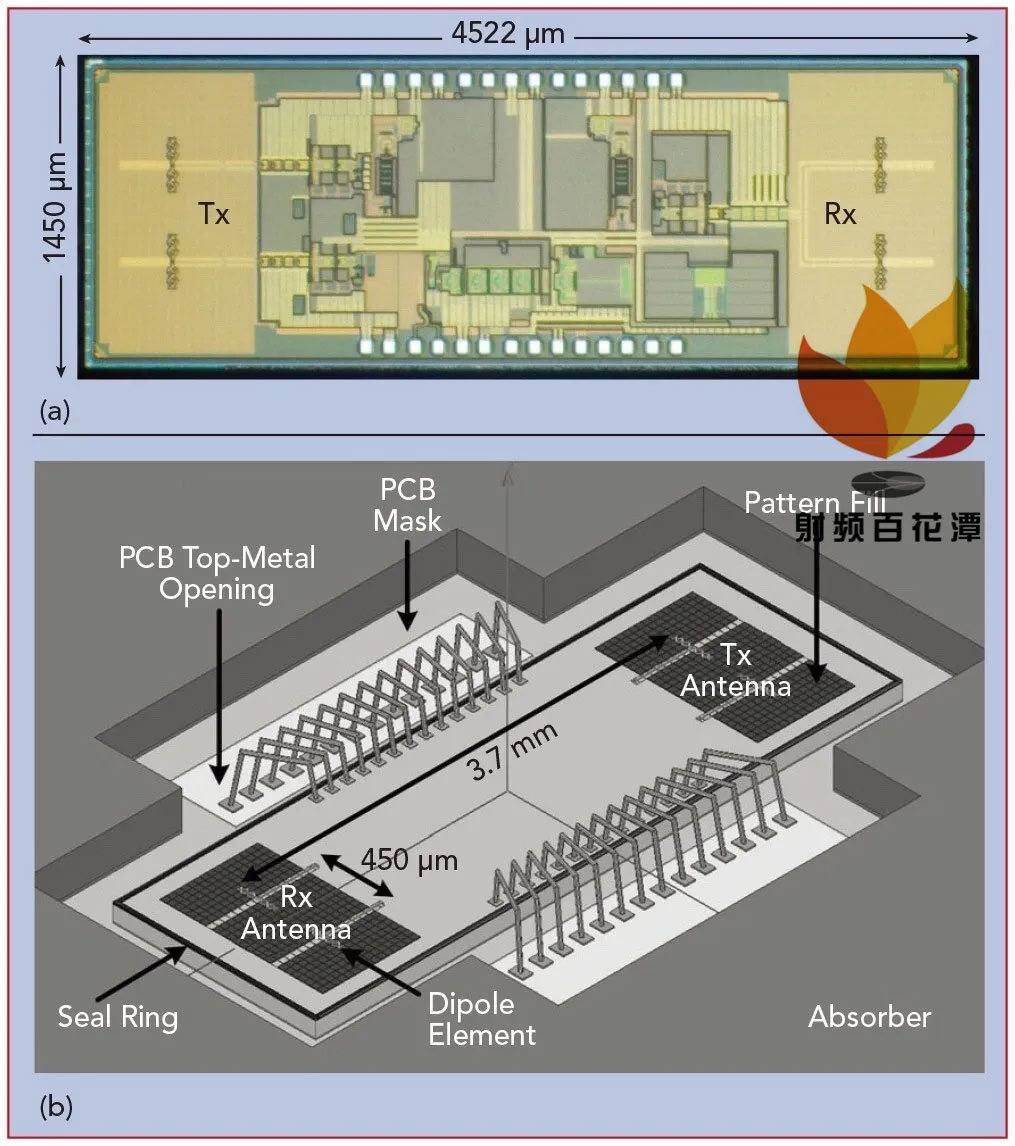

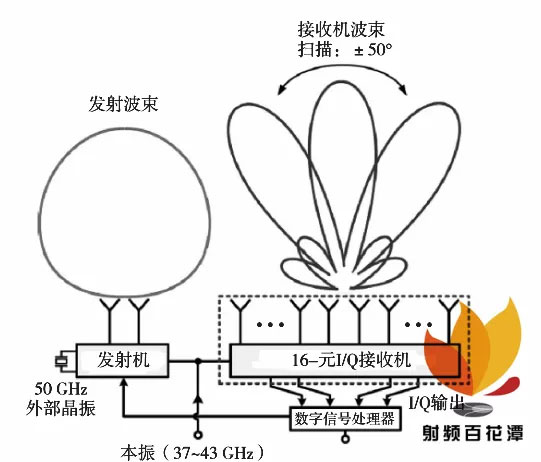

The application range of silicon millimeter wave phased array technology in 5G communications continues to expand. Many companies use SiGe and CMOS processes to make ICs, and their operating frequencies have reached 60-100 GHz. For example, Toyota Research Institute in North America has developed a SiGe single-chip automotive phased array receiver with RF beamforming capability [1], as shown in Figure 1.

The automotive phased array receiver is packaged with low-cost bond wire technology and connected to a 16-element linear microstrip array. The antenna has a directivity of 29.3 dB at a frequency of 77 to 81 GHz, a gain of 28 dB, and can scan to ±50° in the azimuth plane per step (1°). In this chip, the spacing of the planar phased array antenna array is only 0.5λ (λ=3.75 mm, frequency below 80 GHz). This parameter is especially important for millimeter wave circuits with a small usable area. This kind of phase array needs to integrate as many circuits as possible on SiGe or CMOS chips, including not only phase shifters and VGAs, but also all transmit/receive circuits, power synthesis networks, digital and SPI control, and bias circuits. In some cases, a complete up/down converter is also included.

2 Antenna integration technologyCurrently, 60 GHz packaged antennas and on-chip antennas are designed using commercial electromagnetic simulation software. For hybrid solutions, modeling methods that complement standard IC design tools have been developed to achieve coordinated integration of wire bonding and IC. AiP technology requires a broadband low-loss interconnection design between IC and antenna to ensure overall performance. AoC technology requires advanced post-processing steps or packaging processes to reduce severe dielectric loss. Hybrid antenna integration technology combines the advantages of AiP and AoC to achieve high radiation efficiency without the need for low-loss interconnection design of chips and packages. However, the design flexibility of this scheme is not high, and the radiation zero point appears in the wide side direction, which prevents its application in some occasions.

2. 1 AiP technology

2. 1. 1 Structure

AiP technology is a key technology for integrating one-element or multiple-element antennas into the RF package, and its typical solution is to use integrated circuit packaging technology. In the silicon millimeter wave transceiver, the antenna array is integrated in the package to help provide sufficient signal gain and minimize the size. This process is the key technology for the large-scale application of millimeter-wave RF integrated solutions. For example, the size of a 30 GHz antenna element is on the order of millimeters, and a new type of antenna array integration technology needs to be adopted in a single package. The tiny phased array antenna with beam steering function is the key component of millimeter wave radio [2]. In order to integrate the antenna array in the transceiver package, it is necessary to consider the chip assembly scheme, array elements and feeder network, chip and package interconnection, packaging materials, etc. If the transceiver adopts a multi-layer package, it is necessary to adopt advanced interconnection technology between the chip and the antenna to meet the minimum requirement of antenna feed insertion loss. The chip can be placed on the front of the package or on the bottom of the package.

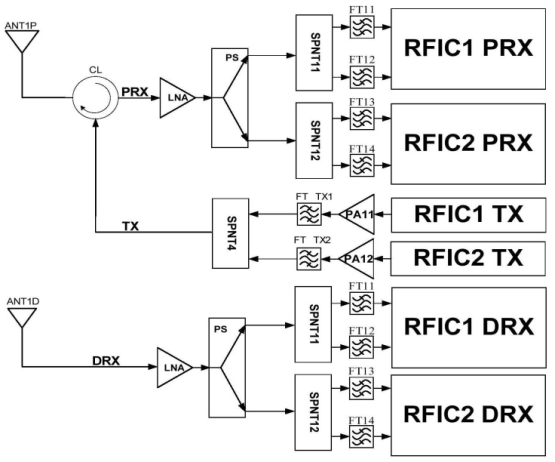

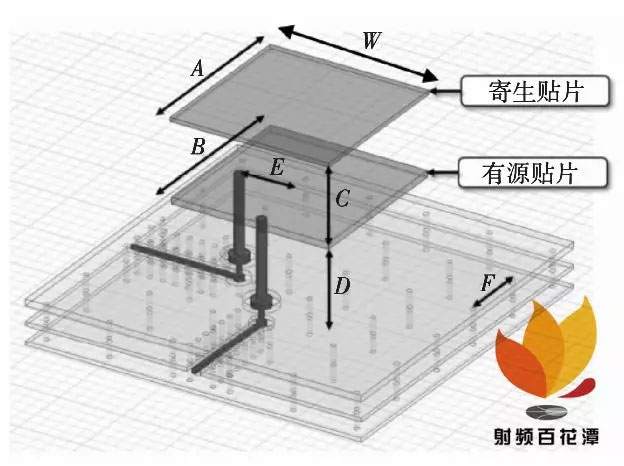

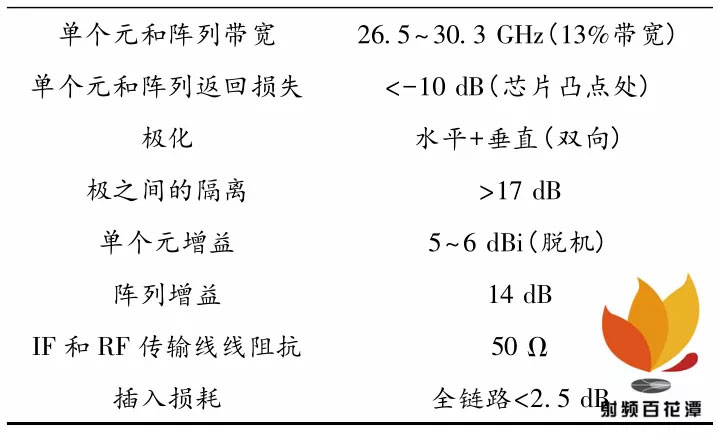

The solution of placing the chip on the bottom of the package has the least impact on chip reception and transmission. A phased array millimeter wave antenna in an organic chip package that can be used for 5G wireless communication is shown in Figure 2. In order to improve the antenna bandwidth, gain and radiation efficiency, a parasitic plane structure is placed on a thick cover plate to form a dual patch antenna stack. In order to achieve the goal of optimizing RF design and manufacturing, the parameters of package laminates and low dielectric constant materials have been optimized, as shown in Table 1.

In AiP design, in addition to beamforming, signal amplification and phased array IC with frequency conversion functions, antennas with polarization characteristics are also key components of the antenna array. In the earliest silicon-based millimeter-wave IC design and development stage, the antenna design uses technologies that are compatible with silicon-based millimeter-wave ICs in terms of substrate, shape and cost [3]. At present, there are millimeter wave antennas on silicon substrates with multiple frequencies. However, due to the large area and limited emission efficiency, antennas above 100 GHz have research value. In 60 GHz frequency, in liquid crystal polymer (LCP), organic high-density interconnect substrate, glass substrate, high/low temperature co-fired ceramic substrate, silicon substrate and molding material-based wafer-level substrate The silicon phased array antenna array fabricated on has been reported. It is usually necessary to optimize the gain, bandwidth and radiation pattern of the AiP array. At the same time, factors such as substrate material, array size (that is, the number of components and patches), interconnection flexibility (such as connecting power and control signals), compatibility of thermal and mechanical properties, IC assembly and board integration need to be considered .

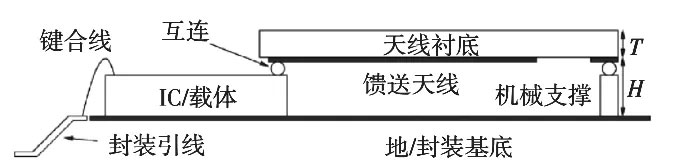

A new antenna and IC/carrier structure is shown in Figure 3 [4]. The antenna structure is fabricated on a dielectric substrate with a thickness of T through a PCB board, and is suspended upside down, flipped over the IC/carrier. The ground of the IC package base is also used as the mirror ground of the antenna, and the distance between the antenna and the ground is H. In this structure, there is a very low dielectric constant between the antenna and the floor, and a layer of cover material with a higher dielectric constant is placed on the antenna structure. On the premise of maintaining high antenna efficiency, this stacked structure has a higher bandwidth than standard PCB antenna structures. A pad with solder balls can be placed on the other end of the antenna cover as a support.

Figure 3 Antenna and IC/carrier structure

In AiP design, integrated circuit packaging technology is usually used for packaging, and the antenna needs to be physically connected to the on-chip circuit. The low-temperature co-fired ceramic (LTCC) process can realize any number of layers of mounting structure, with the flexibility of cross-layer vias, formation of open or closed cavities between layers (IC can be integrated here). The millimeter wave antenna packaged by this process has attracted more and more attention [5]. Some solutions use traditional bonding wire, flip chip and C4 soldering processes. For example, a 60 GHz silicon phased array chip package requires a multi-layer millimeter wave substrate with a low-loss distribution network between the chip and the antenna. It must be a multi-layer low-loss Teflon-based or LTCC-based, which is expensive. Therefore, the typical silicon phased array AiP can reach a frequency of 30 to 60 GHz [6], and it is more difficult to reach 80 GHz.

Compared with the LTCC package solution, the printed circuit board (PCB) package solution can reduce costs. There are packaging schemes that use low-cost high-frequency circuit materials such as PCBs to make multilayer mounting structures, such as the RO3000 series and RO4000 series [7-8]. There is also a low-cost solution using liquid crystal polymer as the substrate. However, due to the use of blind vias or buried vias, the number of layers increases, which will increase the mechanical manufacturing cost of PCB technology. In addition, it is more difficult for PCB technology to achieve high-density in extremely high frequency bands, which will seriously affect system performance and result in reduced efficiency. Therefore, the LTCC process is the choice of most multi-layer structure arrays, and the performance of antennas using this process scheme is improved.

As the carrier frequency and bandwidth move to Asia-Pacific Hertz, the high bandwidth and high carrier frequency make the metal leads become unstable, and the on-chip antenna is considered to be one of the methods to replace the metal interconnection of the chips on the printed board. In addition to on-chip antennas, on-chip waveguides and through-silicon vias (TSV) waveguides are also promising technologies for replacing metal wiring in large bandwidth applications in the Asia-Pacific Hertz band. The successful implementation of on-chip antennas will benefit many applications such as highly integrated transceivers, 60 GHz space power supply combinations and higher frequency millimeter wave systems. There have been many reports on on-chip antennas with multiple frequencies ranging from 0.9 GHz [11] to 77 GHz [12]. The German Institute of High-Performance Microelectronics (IHP) designed and fabricated a 130 GHz on-chip antenna using standard SiGe BiCMOS technology, with a peak gain of 8.4 dBi.

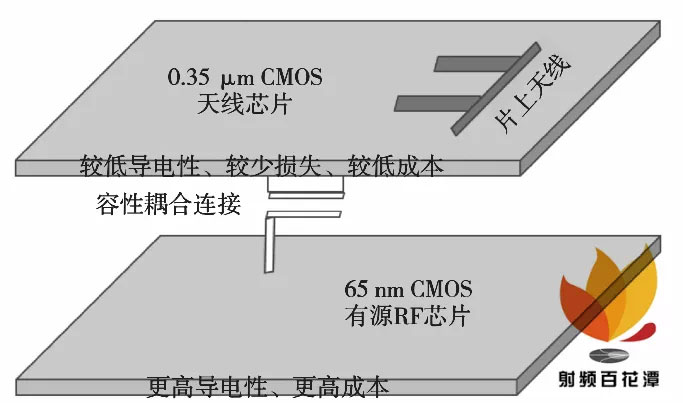

Generally, on-chip antennas fabricated on doped silicon substrates are only about 10% inefficient. However, if a higher cost package antenna is used, higher efficiency can be achieved than on-chip antennas. Capacitive coupling and other advanced connection technologies can be used to connect the antenna chip made on a mature, low-cost, and less-doped substrate with an active 60 GHz millimeter-wave RF chip, so as to achieve a better device than the standard bonding process Much higher operating frequency range. The antenna can be made with a low-cost process (such as 0.18 or 0.35 μm) and a low-doped substrate, and then connected to active components such as a 60 GHz power amplifier through capacitive coupling. Using more advanced technology [20]. A millimeter-wave integrated antenna that connects the antenna chip and the active 60 GHz RF chip through capacitive coupling is shown in Figure 4. The antenna not only has the low conductivity and low loss substrate due to the low doping concentration and high resistivity of the old process, but also has higher efficiency. When making antenna arrays, low-speed active switches (such as diodes) can be integrated on the chip, and phase-divided passive feeders are used to perform component tuning, phase shifting and wave speed control.

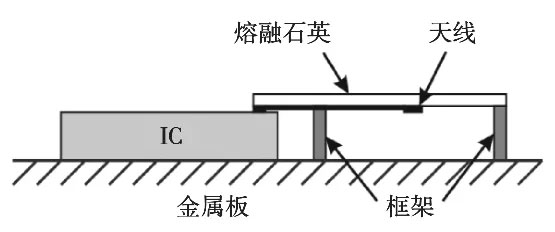

2. 3 Hybrid integrated millimeter wave antennaThe hybrid integrated millimeter wave antenna uses a dedicated process to integrate the antenna and the front-end IC in the same package. This production technology is an alternative to pure AiP and AoC. The schematic diagram of the hybrid integrated antenna is shown in Figure 5 [21]. One half of the dipole antenna on the fused silica substrate is mounted on the chip, and the other half is mounted under the chip. The antenna of this structure can be directly connected to on-chip electronic devices. In the full frequency band of 60 GHz, when the gain is 6-8 dBi, the maximum radiation efficiency of the chip can reach 90%.

3 Progress in millimeter wave antenna integration technology

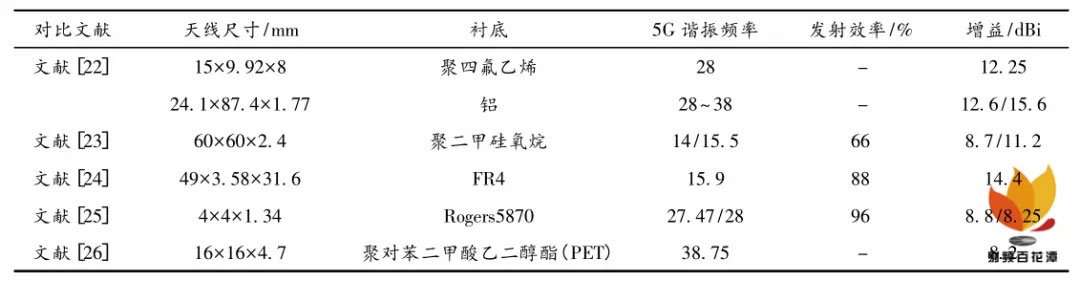

3. 1 The development of academiaTo achieve the goal of comprehensive interconnection between the Internet of Things (IoT) and 5G, it is necessary to develop antennas in different millimeter wave frequency bands and achieve commercial mass production. Table 2 summarizes the millimeter wave antennas and their performance comparisons in recent literature for wide-area IoT and 5G wireless communications. It can be seen that there are still few practical solutions, and most solutions still need to solve the problems of complex structure, reduced gain, low efficiency and high power consumption.

60 GHz millimeter wave band devices will be applied to 5G and mass production. The development trend of system-on-chip or on-chip front-end miniaturization system integration requires that the cost, size, and power consumption of AoC devices and AiP devices must be developed in a smaller direction without sacrificing radiation efficiency, bandwidth, and gain. The use of silicon IC technology provides maximum integration, low cost, and low power consumption, indicating that GaAs and other III-V compound processes are not necessarily the best choice, especially when packaging, integration, and interconnection issues are considered.

IBM has developed the RFIC and AiP series in the past 14 years: performance-driven phased arrays with beamforming and beam scanning capabilities for imaging and communication applications (such as 60 GHz, 94 GHz and 28 GHz phased arrays), supporting portability The device’s V-band, W-band and Ka-band millimeter wave modules (such as 60 GHz single element, switched beam module) [27].

Literature [28] proposed a linearly polarized 6 GHz antenna array constructed on a multilayer LTCC substrate. These arrays use 4×4 microstrip patch radiating elements, respectively fed by a quarter-wavelength matched T-connector network and a Wilkinson power divider network. The measurement results show that the array fed by the former performs better than the array fed by the latter. For arrays with and without embedded cavities, the measured impedance bandwidths are 9.5% and 5.8%, and the maximum gains are 18.2 dBi and 15.7 dBi, respectively.

Literature [29] reported a linearly polarized 60 GHz antenna array constructed on a fused silica substrate. The array uses 2×4 microstrip patch radiating elements fed by a feed network, which uses coplanar strips and coplanar strip waveguides. The array enhanced by the metal cavity achieves a measurement impedance bandwidth greater than 9 GHz and a maximum gain of about 15 dBi.

Literature [30] proposed an antenna array with 2×2 microstrip patch radiating elements using LTCC technology to produce a 60 GHz transmitter module with linear polarization.

Literature [31] used 1×8 and 2×5 microstrip patch radiating elements to fabricate two active linearly polarized 60 GHz antenna arrays.

Literature [32] proposed a linearly polarized 60 GHz antenna array with slot radiating elements fed by a wave-back waveguide network.

Literature [33] proposed a circularly polarized 60 GHz antenna array, which achieved a wide bandwidth by finely designing the original antenna elements, laminated waveguides, and adjusting the circular polarization axis ratio.

Literature [34] proposed a circularly polarized 60 GHz antenna array fabricated on an LCP substrate. The array uses a new slot radiating element and a novel open-cavity reflector. The measurement results show that the peak gain of the 2×4 radiating element array is 15. 6 dBic.

3.2 Development trend of commercialization

According to Gartner’s forecast, by 2021, 9% of smartphones in the market will support 5G networks. 5G uses beamforming technology and must use a multi-antenna array system (Massive MIMO). This will lead to an order of magnitude increase in antennas, and promote the development of antennas in a highly integrated and complex direction, with continuous upgrading of process technology and continuous application of new materials. For example, the new material liquid crystal polymer (LCP) material has the advantages of low loss, high flexibility, high sealing, etc., which is very suitable for making microwave and millimeter wave devices. The millimeter wave antenna solution introduced by Apple includes antennas made of LCP materials, which is an important direction for the large-scale commercialization of 5G antennas [35]. Qualcomm’s QTM052 millimeter wave antenna module series supports compact package size and is suitable for mobile terminal integration. Terminals equipped with QTM052 millimeter-wave antenna modules will be launched on the market in the first half of 2019, showing the development trend of integrating antennas and RF front-end components in 5G. STMicroelectronics, STATS ChipPAC and Infineon Technologies have jointly developed the next generation eWLB semiconductor product packaging technology based on Infineon’s first-generation embedded wafer level ball grid array (eWLB) technology. A four-channel transceiver made of an integrated antenna with an 8 mm×8 mm package has been developed. The antenna adopts the metal structure in the RDL layer and is integrated in the package, providing a solution for radar system packaging applied in the millimeter wave field such as 5G [36]. Recently, SMIC released the world’s first ultra-wideband dual-polarized 5G millimeter wave antenna chip wafer-level integrated package made on the SmartAiPTM process platform. It has the characteristics of high integration, good heat dissipation, and simple process. Realize 24-43 GHz ultra-wideband signal transmission and reception, and achieve an ultra-high antenna gain of 12. 5 dB.

4 Conclusion

For a long time in the future, the 5G architecture will continue to evolve in the network, wireless access, and physical layers. It is necessary to have a variety of innovative product combinations in RF/millimeter wave integrated circuits, millimeter wave antenna array technology, etc., to promote 5G Radio and industrialization development. For example, the number of power amplifiers, antennas, filters, and matching circuits in 5G can be as high as 64 or more. The improvement in efficiency and integration of these components is very important to the overall energy efficiency and performance of the radio. A highly integrated MIMO radio with a large number of antennas and a frequency of 27 GHz and above is the key technology of the 5G system. The above three integrated solutions can be used for millimeter wave antenna design. Taking the 60 GHz frequency band as an example, the radiation efficiency and gain indicators of AoC devices lag behind AiP devices and hybrid solutions. AiP devices and hybrid devices achieve the best radiation efficiency, so it can be considered that AiP technology is more appropriate than AoC technology. AiP technology has the advantages of design flexibility and printed antenna structure, but for complex multilayer packaging structures, it may not have the conditions to compete with AoC technology and hybrid solutions at the same cost. In addition, the chip-to-chip interconnection of the AiP solution will cause heat loss, delay, and increased design effort. The hybrid solution seems to be the best solution. However, when the frequency exceeds 60 GHz, the typical hybrid technology and AiP are not mature solutions. The AoC program will be more complete and has been tested in the THz band. It is expected that the AoC program has more room for development at high frequencies.

A fundamental solution for antenna integration is to integrate everything required for a phased array on a chip, which is the advantage of the silicon-based millimeter wave antenna system. Not only integrated electronic devices, but also integrated high-efficiency antennas leading to wafer-level implementation. The wafer-level phased array can be placed on a low-cost printed circuit board with input/output data signals up to Gbit/s and arranged with control devices and power devices. The entire millimeter wave function is integrated on the same chip. This wafer-scale implementation is a completely self-contained solution. (References omitted)

Author: Wang Wenjie, Qiu Sheng, Wang Jianan, Lai Van